# 2023 Embedded Systems Week

17-22 September 2023 | Hamburg, Germany

### **2023 ESWEEK PROGRAM**

#### SPONSORING SOCIETIES:

#### **WELCOME TO ESWEEK 2023**

Sharon Hu General Chair U. of Notre Dame, USA

Alain Girault Vice-General Chair INRIA, France

Heiko Falk Local Chair TU Hamburg, Germany

#### Welcome to ESWEEK 2023 in Hamburg!

Embedded Systems Week (ESWEEK) is the premier event covering all aspects of embedded systems and software. By bringing together three leading conferences (CASES, CODES+ISSS, and EMSOFT), two symposia, three hot-topic workshops, four special sessions, six tutorials, thirteen education classes, three software competitions with demos, and a special program on Diversity, Equity and Inclusion, ESWEEK presents attendees a wide range of choices unveiling state of the art embedded systems design and hardware/software architectures. Besides, ESWEEK 2023 features a special day program on the topic of semiconductor renaissance and its impact on embedded systems design.

Following the journal-integrated publication model for the three conferences (CASES, CODES+ISSS, and EMSOFT), all regular papers presented are published in the ACM Transactions on Embedded Computing Systems. In addition, authors had the possibility to publish Late Breaking papers in IEEE Embedded Systems Letters, and Work-in-Progress papers in the ESWEEK Proceedings.

The technical program on Monday, Tuesday, and Wednesday consists of 20 regular sessions and 2 special sessions from the three conferences. A strong emphasis on interaction is ensured thanks to a poster presentation for each paper, during which the participants can discuss the papers with the authors.

On Tuesday we have the semiconductor renaissance special day, focusing on the one hand on Green IoT and Green ICT for the Green Transition (the morning special session), and on the other hand on Machine Learning for Embedded System Design (afternoon special session).

Highlights of the ESWEEK program are three keynote talks by distinguished leaders in academia and industry. On Monday morning, Prof. Sarita Adve, from the University of Illinois at Urbana-Champaign, will give a talk on era of immersive computing and how it will shape the research agenda for embedded systems. Then, on Tuesday Morning, Dr. Heike Riel, IBM fellow from IBM Research Europe in Zurich, will give a talk on how to scale quantum computing. Finally, on Wednesday morning, Prof. Lothar Thiele, from ETH Zurich, will give a talk on resilient embedded systems in the era of machine learning.

Two panels will take place: An Industry Panel on Tuesday afternoon (just before the social event), dedicated to the links between the semiconductor industry and embedded computing, and an education panel on Wednesday afternoon

exploring the links between computer engineering education, embedded computing, and the semiconductor renaissance.

The Test of Time Award ceremony will take place on Tuesday morning to honor the authors of articles published in previous editions of ESWEEK (respectively CASES 2008, CODES+ISSS 2007, and EMSOFT 2007), and having the highest impact. Regarding the Best Paper ceremony, it will take place on Wednesday morning, the best papers for the three conferences being selected from candidate papers presented during Monday and Tuesday regular sessions.

Thursday and Friday are the days for the symposia and workshops. We are excited to host two symposia: MEMOCODE (International Symposium on Formal Methods and Models for System Design) and NOCS (International Symposium on Networks on Chip). We are also excited to host three workshops: CODAI (Workshop on Compilers, Deployment, and Tooling for Edge AI), DOT-PIM (Workshop on Agile Design and Optimization Tools for Processing-In-Memory), and RSP (Workshop on Rapid System Prototyping).

The tutorials on Sunday precede the conferences and are an excellent opportunity to get in-depth knowledge in new trends and hot topics. There are four half-day and two full-day tutorials, covering a wide scope of topics, including high-level synthesis, model-checking, runtime monitoring and management, and hw/sw codesign. Two of these tutorials are sponsored by industry, AMD and Siemens.

On Thursday and Friday the week before (September 14<sup>th</sup> and 15<sup>th</sup>), thirteen education classes will take place, given prominent experts in embedded systems, and available virtually. These are excellent opportunities for students and young researchers to improving their knowledge in these topics.

We are grateful to our ACM (SIGBED, SIGDA, SIGMICRO) and IEEE (CEDA and CASS) sponsors as well as the following industry sponsors: AMD, NXP, Synopsys, Huawei, Bosch, and Siemens. The organization of ESWEEK was only possible with the continuous support and help from many volunteers: The program chairs with their program committee members, the organizers of the special day, the workshops, tutorials, and symposia, all members of the organization committee, and, last but not least, the local arrangement team.

After three years of virtual conference, we are looking forward to meeting you in person at ESWEEK 2023 in Hamburg!

### **ESWEEK 2023 THANK YOU TO OUR SPONSORS**

### **GOLD**

#### **BRONZE**

#### **TUTORIAL**

## **SIEMENS**

#### SPONSORING SOCIETIES

| Thursday, September 14 |                                                                                                        | Education Classes                                                                              |                                                                                                   |                                                                                |

|------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                        | Virtual                                                                                                | Virtual                                                                                        | Virtual                                                                                           | Virtual                                                                        |

| 10:00-12:00            | Jian-Jia Chen TU Dortmund Data Flow from Cause to Effect in Distributed Systems: Data Age and Reaction | Preeti Ranjan Panda<br>IIT Delhi<br>3D Memory - Thermal<br>Challenges and System<br>Management |                                                                                                   |                                                                                |

| 16:00-18:00            | Edward Lee UC, Berkeley Deterministic Concurrency and the Lingua Franca Coordination Language          | Yiran Chen Duke Efficient and Robust Edge Al: Software, Hardware, and the Co-design            | Umit Ogras Wisconsin A Novel Runtime Environment for Accelerator-Rich Heterogeneous Architectures | Aviral Shrivastava Arizona State Basics of Machine Learning Accelerator Design |

| Frida       | ay, September 15                                                                                                      |                                                                                               | Education Classes                                                                                                   | 5                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|             | Virtual                                                                                                               | Virtual                                                                                       | Virtual                                                                                                             | Virtual                                                                           |

| 10:00-12:00 | Tulika Mitra National University of Singapore Coarse-Grained Reconfigurable Array (CGRA): Architectures and Compilers | Soonhoi Ha Seoul National University Design Methodology for Low Power Computer Vision Systems | Fabrizio Ferrandi Politecnico di Milano Antonino Tumeo PNNL High-Level Synthesis of Complex Parallel Specifications |                                                                                   |

| 16:00-18:00 | Jan Rabaey UC, Berkeley Marian Verhelst KU Leuven Bringing ML to the Extreme Edge                                     | Sudeep Pasricha Colorado State Optical Computing for Al Acceleration                          | Éricles Sousa and Felipe Augusto da Silva Cadence The Five Must-have Features of Automotive SoC Architectures       | Diana Goehringer TU Dresden Self-Adaptive Domain- Specific Computer Architectures |

| Sund          | ay, September                                                                                                                                                    | · 17                                                                                                                                  | Tutorials and                                                                                                                                                                                                                                  | Diversity Eve                                                                                                                                                                        | ents                                                                                                                                                                                                                                                                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

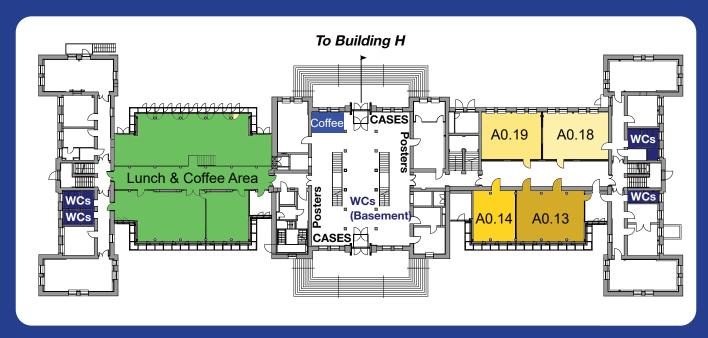

|               | A0.18                                                                                                                                                            | A0.14                                                                                                                                 | A1.19                                                                                                                                                                                                                                          | A0.19                                                                                                                                                                                | A0.13                                                                                                                                                                                                                                                                                              |

| 09:00 - 10:30 | Tutorial 1:<br>Introduction to the<br>AMD Versal ACAP<br>Adaptable Intelligent<br>Engine and to its<br>Programming Model<br>Mario Ruiz, Cathal<br>McCabe, AMD    | Tutorial 2: Designing<br>an Edge Inferencing<br>Accelerator using<br>High-Level Synthesis<br>Petri Solanti, Russell<br>Klein, Siemens | Tutorial 3: How to Use Model Checking to Analyze Circuits at the Transistor Level Michael Raitza, Steffen Märcker, TU Dresden                                                                                                                  | Tutorial 5: MARS: A framework for runtime monitoring, modeling, and management of realtime systems Bryan Donyanavard, Biswadip Maity, Tiago Mück, UC Irvine, Arm and San Diego Univ. |                                                                                                                                                                                                                                                                                                    |

| 10:30 - 11:00 |                                                                                                                                                                  |                                                                                                                                       | Coffee Break                                                                                                                                                                                                                                   |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                    |

| 11:00 - 12:30 | Tutorial 1:<br>Introduction to the<br>AMD Versal ACAP<br>Adaptable Intelligent<br>Engine and to<br>its Programming<br>Model<br>Mario Ruiz, Cathal<br>McCabe, AMD | Tutorial 2: Designing<br>an Edge Inferencing<br>Accelerator using<br>High-Level Synthesis<br>Petri Solanti, Russell<br>Klein, Siemens | Tutorial 3: How to Use Model Checking to Analyze Circuits at the Transistor Level Michael Raitza, Steffen Märcker, TU Dresden                                                                                                                  | Tutorial 5: MARS: A framework for runtime monitoring, modeling, and management of realtime systems Bryan Donyanavard, Biswadip Maity, Tiago Mück, UC Irvine, Arm and San Diego Univ. |                                                                                                                                                                                                                                                                                                    |

| 12:30 - 13:30 |                                                                                                                                                                  |                                                                                                                                       | Lunch Break                                                                                                                                                                                                                                    | 3000                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                    |

| 13:30 - 15:00 | Tutorial 1:<br>Introduction to the<br>AMD Versal ACAP<br>Adaptable Intelligent<br>Engine and to its<br>Programming Model<br>Mario Ruiz, Cathal<br>McCabe, AMD    | Tutorial 2: Designing<br>an Edge Inferencing<br>Accelerator using<br>High-Level Synthesis<br>Petri Solanti, Russell<br>Klein, Siemens | Tutorial 4: Neural<br>Network and<br>Autonomous Cyber-<br>Physical Systems<br>Formal Verification<br>for Trustworthy<br>Al and Safe<br>Autonomy<br>Hoang-Dung Tran,<br>Diego Manzanas<br>Lopez, Taylor T.<br>Johnson, Vanderbilt<br>University | Tutorial 6: HW/<br>SW Codesign for<br>Brain-Inspired<br>Hyperdimensional In-<br>Memory Computing<br>Paul R. Genssler,<br>Simon Thomann,<br>Hussam Amrouch, TU<br>Munich              | Diversity, Equity<br>and Inclusion in<br>Embedded Systems<br>Research<br>An overview of the<br>EUGAIN COST Action:<br>A European Network<br>for Gender Balance<br>in Informatics<br>(13h30-14h)<br>Panel I (14h-15h):<br>Career perspectives in<br>academia vs. industry                           |

| 15:00 - 15:30 |                                                                                                                                                                  |                                                                                                                                       | Coffee Break                                                                                                                                                                                                                                   |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                    |

| 15:30 - 17:00 | Tutorial 1:<br>Introduction to the<br>AMD Versal ACAP<br>Adaptable Intelligent<br>Engine and to its<br>Programming Model<br>Mario Ruiz, Cathal<br>McCabe, AMD    | Tutorial 2: Designing<br>an Edge Inferencing<br>Accelerator using<br>High-Level Synthesis<br>Petri Solanti, Russell<br>Klein, Siemens | Tutorial 4: Neural<br>Network and<br>Autonomous Cyber-<br>Physical Systems<br>Formal Verification<br>for Trustworthy Al<br>and Safe Autonomy<br>Hoang-Dung Tran,<br>Diego Manzanas<br>Lopez, Taylor T.<br>Johnson, Vanderbilt<br>University    | Tutorial 6: HW/<br>SW Codesign for<br>Brain-Inspired<br>Hyperdimensional<br>In-Memory<br>Computing<br>Paul R. Genssler,<br>Simon Thomann,<br>Hussam Amrouch, TU<br>Munich            | Diversity, Equity and Inclusion in Embedded Systems Research Overview of the EUGAIN COST action (13h30-14h): Rukiye Altin Panel I (14h-15h): Diversity initiatives – are we on the right path? Panel II (15h30-16h30): Carreer perspectives in academia vs. industry Mentoring session (16h30-17h) |

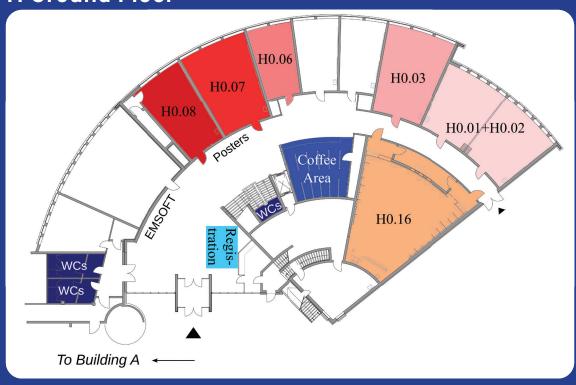

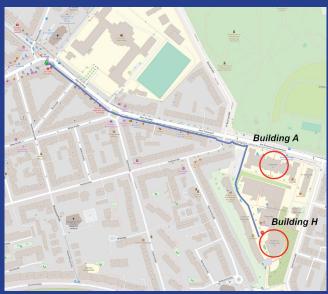

| 18:00 - 19:30 |                                                                                                                                                                  | Reception in the E                                                                                                                    | SWEEK Lunch & Coffee                                                                                                                                                                                                                           | Area in Building A                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                    |

| Mond          | Monday, September 18                                                                                               |                                                                                                                                                              |                                                                                                                                        |                                                                                                                                                                                                                                 |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8:30 - 9:00   |                                                                                                                    | Opening Session                                                                                                                                              | on (Audimax 1)                                                                                                                         |                                                                                                                                                                                                                                 |  |

| 9:00 - 10:00  | Enabling the Era                                                                                                   | KEYNOTE 1<br>a of Immersive Computing: A R<br>Prof. Sarita A                                                                                                 | (Audimax 1)<br>ich Agenda for Embedded Sys<br>Adve (UIUC)                                                                              | tems Research                                                                                                                                                                                                                   |  |

| 10:00 - 10:30 |                                                                                                                    | Coffee                                                                                                                                                       |                                                                                                                                        |                                                                                                                                                                                                                                 |  |

|               | A0.13                                                                                                              | H0.01+H0.02                                                                                                                                                  | H0.16                                                                                                                                  | H0.03                                                                                                                                                                                                                           |  |

| 10:30 - 12:00 | CASES 1: Co-Design for ML Accelerators *                                                                           | CODES 1: In-Memory Computing meets EdgeAl *                                                                                                                  | EMSOFT 1: Formal CPS design *                                                                                                          | Image/AI and ESSC competitions                                                                                                                                                                                                  |  |

| 10:30-10:55   | Let Coarse-Grained Resources Be Shared: Mapping Entire Neural Networks on FPGAs Best paper candidate.              | Overflow-free compute<br>memories for edge Al<br>acceleration<br>Best paper candidate.                                                                       | Towards Building Verifiable<br>CPS using Lingua Franca.                                                                                | Segmentation Track: Low-Power<br>Computer Vision Challenge<br>(10:30 - 10:38) ENOT<br>(10:38 - 10:46) AidgetRock<br>(10:46 - 10:54) ModelTC                                                                                     |  |

| 10:56-11:21   | MaGNAS: A Mapping-Aware<br>Graph Neural Architectural<br>Search Framework for<br>Heterogeneous MPSoC<br>Deployment | CRIMP: Compact & Reliable DNNs Inference for In-Memory Processing via Crossbar-Aligned Compression and Non- ideality Adaptation                              | Equation-Directed Axiomatization of Lustre Semantics to Enable Optimized Code Validation Best paper candidate.                         | Classification Track: Fair<br>and Intelligent Embedded<br>System Challenge<br>(10:54 - 11:02) Intelligent<br>and Robotic Systems<br>(11:02 - 11:10) Sustainable<br>Computing Laboratory<br>(11:10 - 11:18) Rutgers Efficient Al |  |

| 11:22-11:47   | GHOST: A Graph Neural<br>Network Accelerator using<br>Silicon Photonics                                            | SpinBayes: Algorithm-<br>Hardware Co-Design for<br>Uncertainty Estimation<br>Using Bayesian In-Memory<br>Approximation on Spintronic-<br>Based Architectures | Verified Compilation of<br>Synchronous Dataflow with<br>State Machines<br>Best paper candidate.                                        | ESSC Competition Track 1:<br>(11:20 - 11:28) gem5-NVDLA:<br>A Simulation Framework for<br>Compiling, Scheduling and<br>Architecture Exploration on Al<br>System-on-Chips                                                        |  |

| 11:48-11:53   | WiP: Error-Compensation-<br>Based Energy-Efficient MAC<br>Unit for CNNs                                            | LB: Differentiable Slimming<br>for Memory-Efficient<br>Transformers                                                                                          | WiP: Searching Optimal Compiler Optimization Passes Sequence for Reducing Runtime Memory Profile using Ensemble Reinforcement Learning | (11:28 - 11:36) ESP: an Open-Source Platform for the Design and Programming of Heterogeneous SoCs (11:36 - 11:44) ARM-CO-UP: ARM Co-Operative Utilization                                                                       |  |

| 11:54-11:59   | WiP: QRCNN: Scalable CNNs                                                                                          |                                                                                                                                                              | WiP: Mixing computation and interaction on FPGA                                                                                        | of Processors (11:44 - 11:52) ZoneTrace: A Zone Monitoring Tool for F2FS on ZNS SSDs (11:52 - 12:00) AutoDiCE Toolkit: Fully Automated Distributed CNN Inference at the Edge                                                    |  |

| 12:00 - 12:30 |                                                                                                                    | Poster S                                                                                                                                                     | Session                                                                                                                                |                                                                                                                                                                                                                                 |  |

| 12:30 - 13:30 |                                                                                                                    | Lunch                                                                                                                                                        | Break                                                                                                                                  |                                                                                                                                                                                                                                 |  |

| 13:30 - 15:00 | CASES 2: Edge<br>Computing                                                                                         | CODES 2: Advanced<br>Trends in Efficient<br>Inference *                                                                                                      | EMSOFT 2: Mobile and resource-constrained systems *                                                                                    | ESSC and SRC competitions                                                                                                                                                                                                       |  |

|               | A0.13                                                                                                                                                  | H0.01+H0.02                                                                                                                                                      | H0.16                                                                                                                                | H0.03                                                                                                                                                                     |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:30-13:55   | Energy-efficient Personalized<br>Federated Search with Graph<br>for Edge Computing                                                                     | Florets for Chiplets: Data Flow-<br>aware High-Performance and<br>Energy-efficient Network-on-<br>Interposer for CNN Inference<br>Tasks<br>Best paper candidate. | DaCapo: An On-Device<br>Learning Scheme for<br>Memory-Constrained<br>Embedded Systems                                                | ESSC Competition Track 2<br>(13:30 - 13:38) Fault Attac<br>Exploitability Detection in<br>Block Cipher Softwares<br>(13:38 - 13:46) HyboGen:<br>A compiler for innovative |

| 13:56-14:21   | ViT4Mal: Lightweight Vision<br>Transformer for Malware<br>Detection on Edge Devices                                                                    | Keep in Balance: Runtime-<br>reconfigurable Intermittent<br>Deep Inference<br>Best paper candidate.                                                              | iAware: Interaction Aware Task Scheduling for Reducing Resource Contention in Mobile Systems                                         | interleaved execution and<br>compilation scenarios<br>(13:46 - 13:54) CPSim:<br>Simulation and Security Toolbo                                                            |

| 14:22-14:47   | CIM: A Novel Clustering-<br>based Energy-Efficient<br>Data Imputation Method for<br>Human Activity Recognition                                         | STADIA: Photonic Stochastic<br>Gradient Descent for Neural<br>Network Accelerators                                                                               | Rectifying Skewed Kernel<br>Page Reclamation in Mobile<br>Devices for Improving User-<br>Perceivable Latency<br>Best paper candidate | for Cyber-Physical Systems (13:54 - 14:02) CHARM: Composing Heterogeneous AcceleRators for End-to-en Deep Learning Inference of Versal ACAP Architecture                  |

| 14:48-14:53   | WiP: Towards Evaluating<br>CNNs Against Integrity<br>Attacks on Multi-tenant<br>Computation                                                            | LB: DynaFuse: Dynamic<br>Fusion for Resource Efficient<br>Multi-modal Machine<br>Learning Inference                                                              | LB: Efficient Partial Weight Update Techniques for Lightweight On-Device Learning on Tiny Flash- Embedded MCUs                       |                                                                                                                                                                           |

| 14:54-14:59   | WiP: Automatic DNN Deployment on Heterogeneous Platforms: the GAP9 Case Study                                                                          |                                                                                                                                                                  | WiP: CLERR: A High-performance<br>Cross-layer Method for<br>Eliminating Rendering<br>Redundancy in Android                           |                                                                                                                                                                           |

| 15:00 - 15:30 |                                                                                                                                                        | Poster Session                                                                                                                                                   | & Coffee Break                                                                                                                       |                                                                                                                                                                           |

| 15:30 - 17:00 | SS 1: Non-Volatile<br>Memories: Challenges and<br>Opportunities for Embedded<br>System Architectures with<br>Focus on Machine Learning<br>Applications | CODES 3: Emerging<br>Embedded Applications<br>- Sustainability, Safety<br>and Learning                                                                           | EMSOFT 3: Networking                                                                                                                 | SRC: ACM<br>Student Research<br>Competition                                                                                                                               |

| 15:30-15:55   | Embedded Systems with<br>Nonvolatile Main Memories<br>- Programming for<br>persistence and memory<br>access time trade-offs                            | A Self-Sustained CPS<br>Design for Reliable Wildfire<br>Monitoring                                                                                               | CrossTalk: Making Low-<br>Latency Fault Tolerance<br>Cheap by Exploiting<br>Redundant Networks                                       |                                                                                                                                                                           |

| 15:56-16:21   | Architecture to compiler co-optimization for computation in resistive non-volatile memories                                                            | BASS: Safe Deep Tissue<br>Optical Sensing for Wearable<br>Embedded Systems                                                                                       | Improving worst-case TSN communication times of large sensor data samples by exploiting synchronization                              |                                                                                                                                                                           |

| 16:22-16:47   | Memory-Centric Machine<br>Learning                                                                                                                     | FedHIL: Heterogeneity Resilient<br>Federated Learning for<br>Robust Indoor Localization<br>with Mobile Devices                                                   | B-AWARE: Blockage Aware<br>RSU Scheduling for 5G<br>Enabled Autonomous<br>Vehicles                                                   |                                                                                                                                                                           |

| 16:48-16:53   | Prospects of Memory-<br>Centric Computing on Flash<br>Memories                                                                                         | WiP: Efficient Gait Trajectory<br>Prediction Method Based<br>on Soft Constraint Weighted<br>Template Matching                                                    | WiP: Efficient TSN network<br>interface handling in a mixed<br>criticality system                                                    |                                                                                                                                                                           |

| 16:54-16:59   |                                                                                                                                                        | WiP: NAPMAE: Generalized Data-Efficient Neural Architecture Predictor with                                                                                       | WiP: Flexible bus arbitration in mixed criticality systems                                                                           |                                                                                                                                                                           |

| Tueso         | Tuesday, September 19                                                                                              |                                                                                                               |                                                                                                          |                                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 8:30 - 9:00   |                                                                                                                    | Test of Time Award                                                                                            | Ceremony (Audimax 1)                                                                                     |                                                                                                                              |

| 9:00 - 10:00  |                                                                                                                    | Scaling Quar                                                                                                  | <b>2</b> (Audimax 1) ntum Computing e Riel (IBM)                                                         |                                                                                                                              |

| 10:00 -10:30  |                                                                                                                    | Coffe                                                                                                         | ee Break                                                                                                 |                                                                                                                              |

|               | A0.13                                                                                                              | H0.01+H0.02                                                                                                   | H0.16                                                                                                    | H Audimax 1                                                                                                                  |

| 10:30 - 12:00 | CASES 3: Embedded<br>Systems Security*                                                                             | CODES 4: Efficient<br>Memory Design and<br>Management                                                         | EMSOFT 4: Real-<br>Time and distributed<br>systems                                                       | Special Day SS1: Green<br>IoT and Green ICT for<br>the Green Transition:<br>Challenges,<br>Opportunities, Recent<br>Research |

| 10:30-10:55   | Protection Window Based<br>Security-Aware Scheduling<br>against Schedule-Based<br>Attacks<br>Best paper candidate. | WARM-tree: Making<br>Quadtrees Write-efficient<br>and Space-economic on<br>Persistent Memories                | Methods to Realize<br>Preemption in Phased<br>Execution Models                                           | (10:30-10.53) Policy implications for the energy transition: Challenges and opportunities from a system perspective          |

| 10:56-11:21   | Predictable GPU Wavefront<br>Splitting for Safety-Critical<br>Systems                                              | IOSR: Improving I/O<br>Efficiency for Memory<br>Swapping on Mobile<br>Devices Via Scheduling<br>and Reshaping | Consistency vs. Availability<br>in Distributed Cyber-<br>Physical Systems                                | (10.53-11:15) Applying Green IoT digitalization for the Green Transition: Research challenges and opportunities              |

| 11:22-11:47   | PReFeR: Physically Related<br>Function based Remote<br>Attestation Protocol                                        | CABARRE: Request<br>Response Arbitration<br>for Shared Cache<br>Management                                    | Probabilistic Reaction Time<br>Analysis                                                                  | (11:15-11:37) Digitalization in action: Use cases and lessons learned                                                        |

| 11:48-11:53   | LB: LOCoCAT: Low-<br>Overhead Classification of<br>CAN bus Attack Types                                            | LB: NvMISC: Towards an<br>FPGA-based Emulation<br>Platform for RISC-V and<br>Non-volatile Memories            | LB: External Timed I/O<br>Semantics Preserving<br>Utilization Optimization for<br>LET-based Effect Chain | (11:37-12:00) Green ICT for<br>energy-efficient data centers,<br>edge AI and IoT systems                                     |

| 11:54-11:59   | LB: Flipping Bits Like a Pro:<br>Precise Rowhammering on<br>Embedded Devices                                       | LB: CNN Workloads<br>Characterization and<br>Integrated CPU-GPU DVFS<br>Governors on Embedded<br>Systems      |                                                                                                          |                                                                                                                              |

| 12:00 - 12:30 |                                                                                                                    | Poste                                                                                                         | r Session                                                                                                |                                                                                                                              |

#### **TTA Awards**

Predictable Programming on a Precision Timed Architecture (CASES 2008) by Ben Lickly, Isaac Liu, Sungjun Kim, Hiren D. Patel, Stephen A. Edwards, and Edward A. Lee. Predator: A Predictable SDRAM Memory Controller (CODES+ISSS 2007) by Benny Akesson, Kees Goossens, and Markus Ringhofer. Scheduling Multiple Independent Hard-Real-Time Jobs on a Heterogeneous Multiprocessor (EMSOFT 2007) by Orlando Moreira, Frederico Valente, and Marco Bekooij.

| Tuesday, September 19 (continued) |                                                                                                                                                                                                                                                                      |                                                                                                          |                                                                                                                            |                                                                                                                |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                   | A0.13                                                                                                                                                                                                                                                                | H0.01+H0.02                                                                                              | H0.16                                                                                                                      | H Audimax 1                                                                                                    |

| 12:30 - 13:30                     |                                                                                                                                                                                                                                                                      | Lunc                                                                                                     | h Break                                                                                                                    |                                                                                                                |

| 13:30 - 15:00                     | CASES 4: Efficient<br>Memory Systems *                                                                                                                                                                                                                               | CODES 5: Security and<br>Reliability                                                                     | EMSOFT 5:<br>Optimization and<br>design of embedded<br>systems                                                             | Special Day SS2:<br>Machine Learning for<br>Embedded System<br>Design                                          |

| 13:30-13:55                       | ZPP: A Dynamic Technique<br>to Eliminate Cache Pollution<br>in NoC based MPSoCs<br>Best paper candidate.                                                                                                                                                             | Thermal Management for<br>3D-Stacked Systems via<br>Unified Core-Memory Power<br>Regulation.             | Sound Mixed Fixed-Point<br>Quantization of Neural<br>Networks                                                              | (13:30-14:00) ML for System-<br>Level Modeling and Design<br>Speaker: Andreas Gerstlauer,<br>UT Austin         |

| 13:56-14:21                       | EMS-I: An Efficient Memory System Design with Specialized Caching Mechanism for Recommendation System Inference                                                                                                                                                      | ANV-PUF: Machine-<br>Learning-Resilient NVM-<br>Based Arbiter PUF                                        | A Constructive State-based<br>Semantics and Interpreter<br>for a Synchronous Data-<br>flow Language with State<br>machines | (14:00-14:30) ML for High-<br>Level Synthesis: Opportunities<br>and Lessons                                    |

| 14:22-14:47                       | Proactive Stripe Reconstruction to Improve Cache Use Efficiency of SSD-Based RAID Systems                                                                                                                                                                            | HEPHAESTUS: Codesigning<br>and Automating 3D<br>Image Registration<br>on Reconfigurable<br>Architectures | Optimal Synthesis of Robust<br>IDK Classifier Cascades                                                                     | (14:30-15:00) Synthesis Prediction: Use Deep Learning to Expedite the Hardware Architecture and Design Process |

| 14:48-14:53                       | LB: Swift-CNN: Leveraging<br>PCM Memory's Fast Write<br>Mode to Accelerate CNNs                                                                                                                                                                                      | LB: Effects of Runtime<br>Reconfiguration on PUFs<br>Implemented as FPGA-<br>based Accelerators          | LB: Optimized Local Path<br>Planner implementation for<br>GPU-accelerated embedded<br>systems                              |                                                                                                                |

| 14:54-14:59                       | LB: No-Multiplication Deterministic Hyperdimensional Encoding for Resource-Constrained Devices                                                                                                                                                                       | LB: Hardware-Software<br>Co-optimization of Long-<br>Latency Stochastic<br>Computing                     | WiP: Unishyper, A Reliable<br>Rust-based Unikernel for<br>Embedded Scenarios                                               |                                                                                                                |

| 15:00 - 15:30                     |                                                                                                                                                                                                                                                                      | Poster Session                                                                                           | n & Coffee Break                                                                                                           |                                                                                                                |

| 15:30 - 17:00                     | Industry Panel (H Audimax 1) The Global Semiconductor Renaissance and Embedded Computing: An Industry Perspective Panelists: Sankar Basu (US NSF), Tobias Helbig (NXP), Heike Riel (IBM), Jin Yang (Intel), Marilyn Wolf (moderator, University of Nebraska Lincoln) |                                                                                                          |                                                                                                                            |                                                                                                                |

| 17:00 - 18:00                     |                                                                                                                                                                                                                                                                      | ESSC Demo                                                                                                | Session (H0.03)                                                                                                            |                                                                                                                |

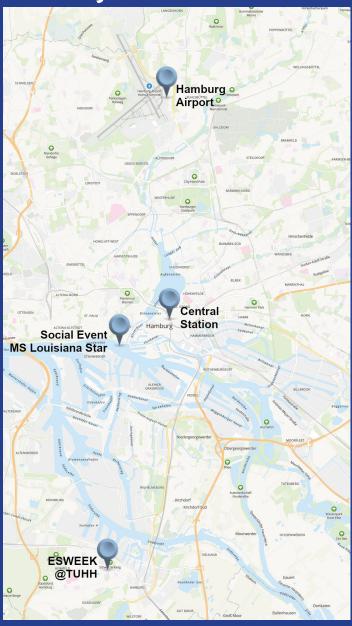

| 19:30 - 23:00                     |                                                                                                                                                                                                                                                                      | Social Event (Dinner cruis                                                                               | se on a "Southern Style" ship)                                                                                             |                                                                                                                |

| Wednesday, September 20 |                                                                                                   |                                                                                                           |                                                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 8:30 - 9:00             |                                                                                                   | Best Paper Award Ceremony                                                                                 |                                                                                                                  |

| 9:00 - 10:00            | KEYNOTE 3: The que                                                                                | est for resilient embedded systems in the<br>Prof. Lothar Thiele (ETH)                                    | era of machine learning                                                                                          |

| 10:00 - 10:30           |                                                                                                   | Coffee Break                                                                                              |                                                                                                                  |

|                         | A0.13                                                                                             | H0.01+H0.02                                                                                               | H0.16                                                                                                            |

| 10:30 - 12:00           | CASES 5: Approximate<br>Computing                                                                 | CODES 6: Data Management for Magnetic Devices                                                             | EMSOFT 6: Learning from black-box components                                                                     |

| 10:30-10:55             | AxOTreeS: A Tree Search Approach<br>to Synthesizing FPGA-based<br>Approximate Operators           | LaDy: Enabling Locality-aware<br>Deduplication Technology on<br>Shingled Magnetic Recording Drives        | Mining Hyperproperties using<br>Temporal Logics                                                                  |

| 10:56-11:21             | VADF: Versatile Approximate Data Formats for Energy-Efficient Computing                           | FSIMR: File-system-aware Data<br>Management for Interlaced Magnetic<br>Recoding                           | Kryptonite : Worst-Case Program<br>Interference Estimation on Multi-Core<br>Embedded Systems                     |

| 11:22-11:47             | Modular DFR: Digital Delayed<br>Feedback Reservoir Model for<br>Enhancing Design Flexibility      | LB (11:22-11:27): Should We Even Optimize for Execution Energy? Rethinking Mapping for MAGIC Design Style | Probabilistic Black-Box Checking via<br>Active MDP Learning                                                      |

| 11:48-11:53             | LB: Vector-Based Dedicated<br>Processor Architecture for Efficient<br>Tracking in VSLAM Systems   | WiP: A Universal Instrumentation<br>Platform for Non-Volatile Memories                                    | WiP: Micro-Accelerator-in-the-Loop<br>Framework for MCU Integrated<br>Accelerator Peripheral Fast<br>Prototyping |

| 11:54-11:59             | LB: An Approximate Parallel<br>Annealing Ising Machine for Solving<br>Traveling Salesman Problems | WiP: A Generic Non-Intrusive<br>Parallelization Approach for SystemC<br>TLM-2.0-based Virtual Platforms   |                                                                                                                  |

| 12:00 - 12:30           |                                                                                                   | Poster Session                                                                                            |                                                                                                                  |

| 12:30 - 13:30           |                                                                                                   | Lunch Break                                                                                               |                                                                                                                  |

| VAI or all so | andre Contomber 20 c                                                                                                                       |                                                                                                                                                                                  |                                                                                                                 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| wean          | esday, September 20 (d                                                                                                                     |                                                                                                                                                                                  |                                                                                                                 |

|               | A0.13                                                                                                                                      | H0.01+H0.02                                                                                                                                                                      | H0.16                                                                                                           |

| 13:30 - 15:00 | CASES 6: Design,<br>Management, and Security of<br>SoCs                                                                                    | SS 2: Mitigating side-channel attacks: A multilayer bottom-<br>up approach                                                                                                       | EMSOFT 7: Design of control systems                                                                             |

| 13:30-13:55   | SpikeHard: Efficiency-Driven<br>Neuromorphic Hardware for<br>Heterogeneous Systems-on-Chip                                                 | (13:30-13:53) Designing SCA-<br>resilient Circuits with Emerging<br>Reconfigurable Nanotechnologies                                                                              | Stochastic Analysis of Control<br>Systems Subject to Communication<br>and Computation Faults                    |

| 13:56-14:21   | DTRL: Decision Tree-based Multi-<br>Objective Reinforcement Learning for<br>Runtime Task Scheduling in Domain-<br>Specific System-on-Chips | (13:53-14:15) Tools for Automated<br>Generation of SCA-Protected Circuits<br>Presenters: Amir Moradi, Ruhr<br>University Bochum, Germany                                         | Formal Synthesis of Neural Barrier<br>Certificates for Continuous Systems<br>via Counterexample Guided Learning |

| 14:22-14:47   | ObNoCs: Protecting Network-on-Chip<br>Fabrics Against Reverse-Engineering<br>Attacks                                                       | (14:15-14:37) Obfuscation against<br>Side-Channel Attacks in Edge<br>Environments<br>Presenters: Chongzhou Fang, Ning<br>Miao, Han Wang, Sai Manoj, Houman<br>Homayoun, UC Davis | Neural Abstraction-Based Controller<br>Synthesis and Deployment                                                 |

| 14:48-14:53   | LB: High Flexibility Designs of<br>Quantized Runtime Reconfigurable<br>Multi-precision Multipliers                                         | (14:37-15:00) Industry Perspectives on<br>Side-Channel Attacks and Defenses<br>Presenters: Benjamin Hettwer, Robert<br>Bosch Corporate Research                                  | WiP: Integrating WebAssembly into<br>Service Oriented Architectures for<br>Edge Systems                         |

| 14:54-14:59   | LB: FPGA Implementation of Modified<br>SNOW 3G Stream Ciphers using Fast<br>and Resource Efficient Substitution Box                        |                                                                                                                                                                                  |                                                                                                                 |

| 15:00 - 15:30 |                                                                                                                                            | Poster Session & Coffee Break                                                                                                                                                    |                                                                                                                 |

| 15:30 - 17:00 | CASES 7: Co-design for ML accelerators                                                                                                     |                                                                                                                                                                                  | Education Panel (H0.16)                                                                                         |

| 15:30-15:55   | Computationally Efficient DNN<br>Mapping Search Heuristic using Deep<br>Reinforcement Learning                                             |                                                                                                                                                                                  | Computer Engineering Education, Embedded Computing, and the Semiconductor Renaissance                           |

| 15:56-16:21   | DASS: Differentiable Architecture<br>Search For Sparse neural networks                                                                     |                                                                                                                                                                                  | Panelists: Robert Dick (University of Michigan), Patrick Haspel (Synopsys),                                     |

| 16:22-16:47   | BitSET: Bit-Serial Early Termination<br>for Computation Reduction in<br>Convolutional Neural Networks                                      |                                                                                                                                                                                  | Jan Madsen (moderator, Danish<br>Technical University), Muhammad<br>Shafique (NYU), Marilyn Wolf                |

| 16:48-16:53   |                                                                                                                                            |                                                                                                                                                                                  | (University of Nebraska Lincoln),                                                                               |

| 16:54-16:59   |                                                                                                                                            |                                                                                                                                                                                  | Wang Yu (Tsinghua University)                                                                                   |

|               | H0.01+H0.02                                                                                               | H0.16                                                                                   | H0.03                                                                                                                                                          | H0.07                                                                                                                   | H0.08                                                                                                    |

|---------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|               | MEMOCODE                                                                                                  | NOCS                                                                                    | Workshop DOT-                                                                                                                                                  | Workshop CODAI                                                                                                          | Workshop RSP                                                                                             |

|               | MEMOCODE                                                                                                  | NOCS                                                                                    | PIM                                                                                                                                                            | (11:00 - 19:00)                                                                                                         | Workshop KSF                                                                                             |

| 9:00 - 10:00  | <b>Keynote 1:</b> Edward A.<br>Lee (U.C. Berkeley)                                                        | Keynote 1: Axel<br>Jantsch (TU Wien)                                                    | Keynote: Memory-<br>Centric Computing<br>(9:45-10:15) Full-stack<br>Deployment and<br>Design tools for RRAM-<br>based Compute-in-<br>memory System             | (10:35 - 11:15)  Keynote: Next- generation Compilers for Emerging Systems                                               | Keynote: Digital<br>Hardware<br>Acceleration for<br>Neural Networks:<br>Implementation<br>Considerations |

| 10:00 -10:30  |                                                                                                           |                                                                                         | Coffee Break                                                                                                                                                   |                                                                                                                         |                                                                                                          |

| 10:30-12:30   | Technical Session 1:<br>Machine Learning                                                                  | Technical Session 1:<br>High-Performance<br>and Dynamic NoC<br>Architectures            |                                                                                                                                                                | Session 1:<br>Deployment and<br>Optimization<br>Techniques                                                              |                                                                                                          |

| 10:30 - 11:00 | Safe Integration<br>of Learning in<br>SystemC using Timed<br>Contracts and Model<br>Checking              | FlooNoC: A Multi-<br>Tbps Wide NoC for<br>Heterogeneous AXI4<br>Traffic                 | A Neuro-Vector-<br>Symbolic Architecture<br>for Data- and<br>Compute-Efficient<br>Continual Learning,<br>Abstract Reasoning,<br>and Combinatorial<br>Inference |                                                                                                                         |                                                                                                          |

| 11:00-11:30   | Hybrid Genetic Reinforcement Learning for Generating Run- Time Requirement Enforcers                      | Dynamically Reconfigurable Network Protocol for Shape-Changeable Computer System        | Opportunities and<br>Challenges for<br>Process-In-Memory<br>(PIM) Technology in<br>ICT Products                                                                | (11:15 - 11:40) Scaling Up Quantization- Aware Neural Architecture Search for Efficient Deep Learning on the Edge       | Fast and Accurate<br>Virtual Prototyping<br>of an NPU with<br>Analytical Memory<br>Modeling              |

| 11:30-12:00   | Robust Testing for<br>Cyber-Physical<br>Systems using<br>Reinforcement<br>Learning                        | PiN: Processing in<br>Network-on-Chip<br>(Tutotial Paper)                               | EDA Toolchain<br>for Processing-<br>in-Memory CNN<br>Accelerators                                                                                              | (11:40 - 12:05) Tiny<br>Machine Learning:<br>Enabling Intelligence<br>on Constrained<br>Devices                         | The Impact of<br>Heterogeneous<br>Logic on Adders and<br>Multipliers in VTR                              |

| 12:00-12:30   | Explaining Unsolvability of Planning Problems in Hybrid Systems with Model Reconciliation                 |                                                                                         |                                                                                                                                                                | (12:05 - 12:30)<br>Hardware-<br>Aware Network<br>Compression: From<br>Data to Silicon                                   | Polynomial Formal<br>Verification Exploiting<br>Constant Cutwidth                                        |

| 12:30 - 13:30 |                                                                                                           |                                                                                         | Lunch Break                                                                                                                                                    |                                                                                                                         |                                                                                                          |

| 13:30 - 15:00 | Technical Session<br>2: Verification<br>and Synthesis                                                     | 2: NoCs for Al<br>Acceleration<br>and Interposer<br>Systems                             |                                                                                                                                                                | Session 2:<br>Compilation<br>Frameworks and<br>Techniques                                                               |                                                                                                          |

| 13:30-14:00   | Allocation and<br>Scheduling of<br>Dataflow Graphs on<br>Hybrid Dataflow/<br>von Neumann<br>Architectures | A NoC-Based Spatial<br>DNN Inference<br>Accelerator with<br>Memory-Friendly<br>Dataflow | (13:30-14:10) HISIM:<br>Heterogeneous<br>Integration Simulator<br>with 2.5D/3D<br>Interconnect<br>Modeling                                                     | (13:30 - 13:55) Accelerating Edge Al with Morpher: An Integrated Design, Compilation and Simulation Framework for CGRAs | (13:30-13:50) SerIOS<br>Enhancing Hardware<br>Security in Integrated<br>Optoelectronic<br>Systems        |

continues on next page

|               | sday, September 21 (continued) Symposia and Workshops                               |                                                                                                                                                  |                                                                                                                                                                                                  |                                                                                                                                                                                                                                       | hops                                                                                                                                                                                                                    |

|---------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|